# GigaDevice Semiconductor Inc.

# **GD32H7xx Power Bypass Mode User Guide**

# Application Note AN225

Revision 1.1

(Feb. 2025)

# **Table of Contents**

| Table of Contents                                | 2  |

|--------------------------------------------------|----|

| List of Figures                                  | 3  |

| List of Tables                                   | 4  |

| 1. Introduction                                  | 5  |

| 2. Introduction to Power Bypass Mode             | 6  |

| 3. Power-up and Power-down Sequence              | 8  |

| 4. Selection of External Power Supply            | 10 |

| 4.1. Using LDO for Power Supply                  | 10 |

| 4.2. The Impact of GPIO on Power Bypass Mode     | 12 |

| 4.3. Optimization Schemes for Power Bypass Mode  | 13 |

| 4.3.1. Use reset chip solution.                  | 13 |

| 5. Precautions for Using External Power Supplies | 14 |

| 6. Revision history                              | 15 |

# **List of Figures**

| Figure 2-1. Bypass Mode (with SMPS Module)                                         | 6            |

|------------------------------------------------------------------------------------|--------------|

| Figure 2-2. Bypass Mode (without SMPS Module)                                      | <del>(</del> |

| Figure 2-3. The software is set to bypass mode                                     | 7            |

| Figure 3-1. Bypass Mode power-up and power-down timing diagram                     | 8            |

| Figure 3-2. Using reset chip to avoid inappropriate power-up and power-down timing | 9            |

| Figure 4-1. Using LDO to supply power to VCORE schematic diagram                   | 11           |

| Figure 4-2. The power-up sequence for supplying power to VCORE using LDO           | 11           |

| Figure 4-3. The power-down sequence for supplying power to VCORE using LDO         | 11           |

| Figure 4-4. Leakage current in GPIO causes oscillation in VCORE voltage            | 12           |

| Figure 4-5. Use a reset chip to prevent misoperation                               | 13           |

# **List of Tables**

| Table 2-1. Bypass Mode register configuration table | 7  |

|-----------------------------------------------------|----|

| Table 4-1. GD30LD1002x Datasheet (Excerpt)          | 10 |

| Table 6-1. Revision history                         | 15 |

### 1. Introduction

This article is specifically designed for engineering personnel developing the GD32H7xx series, mainly introducing the usage methods, precautions, and peripheral component selection for the GD32H7xx power bypass mode. With the development of semiconductor technology, the integration of internal circuits in chips is getting higher and higher, which brings with it an increase in the heat generation density of the chips. As the junction temperature (TJ) of the chip increases, the lifespan of the device will decrease, and the failure rate will also increase accordingly. The GD32H7xx, as a high-performance product of GD32, requires special attention to the high power consumption and heat generation that come with its use. When designing the chip, this product has reserved a power bypass mode, which allows direct power supply to the internal core domain of the MCU from an external power source, avoiding the heat generation caused by the use of internal LDO in extreme environments, which could lead to thermal runaway of the chip.

This article primarily introduces the usage methods, precautions, and peripheral component selection for the GD32H7xx power bypass mode.

#### **Introduction to Power Bypass Mode** 2.

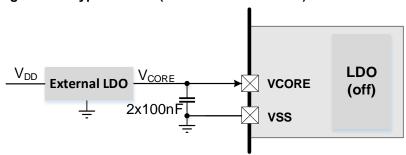

In this mode, the internal SMPS and LDO of the chip are turned off, and the external circuit supplies power to the V<sub>0.9V</sub> domain (core domain) through the VCORE pin. On different packages of the H7 series, the routing of the SMPS pins varies. The BGA176 and LQFP176 packages include the SMPS module, and their SMPS-related pins and VDDLDO pins are both routed out on the package; the LQFP144, LQFP100, and BGA100 packages do not include the SMPS module, and there are no related pins on the package. Therefore, the circuit connection when operating in bypass mode is slightly different, and the specific circuit can refer to Figure 2-1. Bypass Mode (with SMPS Module) and Figure 2-2. Bypass Mode (without SMPS Module) design (when the SMPS module is turned off, the VDDSMPS pin must be connected to VDD or VSS).

**VDDSMPS VLXSMPS SMPS** (off) **VFBSMPS VSSSMPS VDDLDO** LDO  $V_{CORE}$ External LDO **VCORE** (off) 2x100nF **VSS**

Figure 2-1. Bypass Mode (with SMPS Module)

Figure 2-2. Bypass Mode (without SMPS Module)

The configuration method to enter this power supply mode is as follows: the DVSEN bit is set to 0b0, the values of DVSCFG and DVSVC[1:0] have no effect, and the SMPS buck regulator is in the off state; the LDOEN bit is set to 0b0, and the LDO is in the off state; the BYPASS bit is set to 0b1, and the  $V_{0.9V}$  domain is powered by the VCORE pin. The register configuration

for the output voltage of the SMPS and LDO is shown in <u>Table 2-1. Bypass Mode register</u> configuration table:

Table 2-1. Bypass Mode register configuration table

| Symbol | Description      |

|--------|------------------|

| DVSEN  | 0: SMPS disable  |

| LDOEN  | 0: LDO disable   |

| BYPASS | 1: BYPASS enable |

Note: When using the bypass mode for power supply, make sure to switch the power supply mode to bypass mode in the software immediately after the chip initialization; otherwise, there are unforeseeable risks. When programming with the "GD32H7xx\_Firmware\_Library", make settings in the "system\_gd32h7xx.c" file, as shown in *Figure 2-3. The software is set to bypass mode*.

Figure 2-3. The software is set to bypass mode

```

#if defined(GD32H7XXI)

//#define SEL PMU_SMPS_MODE PMU_DIRECT_SMPS_SUPPLY

//#define SEL PMU_SMPS_MODE PMU_LDO_SUPPLY

#define SEL PMU_SMPS_MODE PMU_BYPASS

#elif defined(GD32H7XXZ) | defined(GD32H7XXV)

//#define SEL_PMU_SMPS_MODE PMU_LDO_SUPPLY

#define SEL_PMU_SMPS_MODE PMU_BYPASS

#endif

```

```

#if defined (SEL_PMU_SMPS_MODE)

/* power supply config */

pmu_smps_ldo_supply_config(SEL_PMU_SMPS_MODE);

#endif

/* configure system clock */

system_clock_config();

```

Note: It is recommended to complete the switching of the power mode before configuring the system clock.

### 3. Power-up and Power-down Sequence

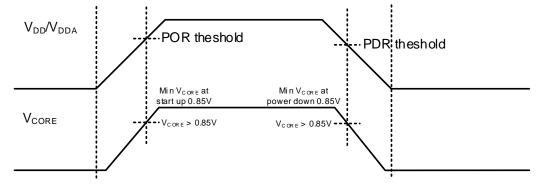

The power-up and power-down sequence requirements for the power bypass mode are as illustrated in *Figure 3-1. Bypass Mode power-up and power-down timing diagram*.

Figure 3-1. Bypass Mode power-up and power-down timing diagram

#### Note:

- 1. Before the MCU's  $V_{DD}/V_{DDA}$  voltage rises to the POR (Power-On Reset) threshold, ensure that the  $V_{CORE}$  voltage is greater than 0.85 V.

- 2. Before the MCU's V<sub>DD</sub>/V<sub>DDA</sub> voltage drops to the PDR (Power-Down Reset) threshold, ensure that the V<sub>CORE</sub> voltage is greater than 0.85 V.

- 3. Under any operating condition, ensure that the V<sub>DD</sub>/V<sub>DDA</sub> voltage is greater than the V<sub>CORE</sub> voltage.

- 4. Be sure to pull the PDR\_ON pin up to VDD to enable the internal POR / PDR function. For details, please refer to the "AN109 GD32H7xx Series Hardware Development Guide."

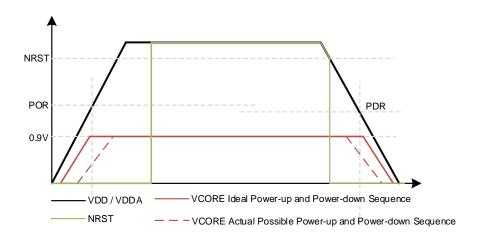

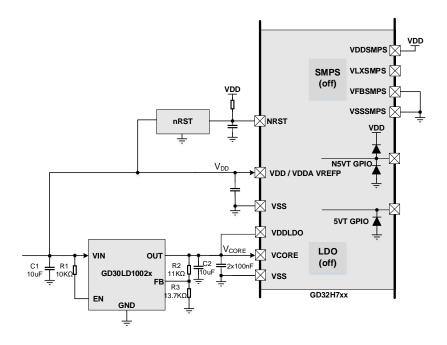

If the external power supply design makes it difficult to meet the timing requirements, a reset chip can be added to avoid the power-up and power-down times, as shown in *Figure 3-2. Using reset chip to avoid inappropriate power-up and power-down timing*The reset chip needs to ensure that VDD / VDDA and VCORE are stable before pulling up during power-up, and to pull down before VCORE drops during power-down. Additionally, the minimum operating voltage of the reset chip should be lower than the Power-Down Reset (PDR) threshold.

Figure 3-2. Using reset chip to avoid inappropriate power-up and power-down timing

# 4. Selection of External Power Supply

### 4.1. Using LDO for Power Supply

Considering power supply stability and ease of controlling the power-up and power-down sequences, it is generally recommended to use an external LDO for power supply in bypass mode. To easily meet the power-up and power-down sequence requirements, the following points are suggested when selecting and using an LDO:

- 1. The input of the LDO is connected to the  $V_{DD}$  terminal.

- The minimum operating input voltage of the LDO, LDO\_VIN<sub>min</sub>, should be less than the MCU's Power-On Reset (POR) and Power-Down Reset (PDR) voltages. The minimum dropout voltage of the LDO plus 0.85V should be less than the MCU's POR and PDR voltages.

- 3. The enable control voltage of the LDO, VEN\_ $H_{min}$ , should be less than the MCU's POR, and VEN\_ $L_{max}$  should be less than the MCU's PDR.

**Note**: For the GD32H7xx MCU, POR = 1.53 V, and PDR = 1.48 V. For detailed information, refer to the datasheet.

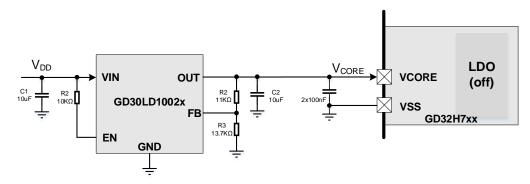

Using the GD30LD1002x as an external power supply for the VCORE pin of the GD32H7xx, the relevant parameters are as shown in *Table 4-1. GD30LD1002x Datasheet (Excerpt)*:

Table 4-1. GD30LD1002x Datasheet (Excerpt)

| Symbol             | Parameter            | Conditions                                          | Min | Тур | Max | Unit |

|--------------------|----------------------|-----------------------------------------------------|-----|-----|-----|------|

| Vin                | Input Range          | -                                                   | 1.4 | ı   | 6.5 | V    |

| Vouт               | Output Voltage Range | _                                                   | 0.5 | -   | 5.2 | V    |

| V <sub>DROP</sub>  | Dropout Voltage      | V <sub>IN</sub> = 1.4 V,<br>I <sub>OUT</sub> =1.2 A | _   | 90  | 150 | mV   |

| V <sub>EN_</sub> H | EN Pin High-Level    | _                                                   | 1.1 | -   | 6.5 | V    |

| V <sub>EN_L</sub>  | EN Pin Low-Level     | _                                                   | 0   | -   | 0.5 | V    |

Its minimum input voltage is 1.4 V, VEN\_ $H_{min}$  = 1.1 V, VEN\_ $L_{max}$  = 0.5 V, supports 0.9 V output, and the maximum output can reach 1.2 A, which meets the selection requirements. For more details, please refer to **www.gigadevice.com**.

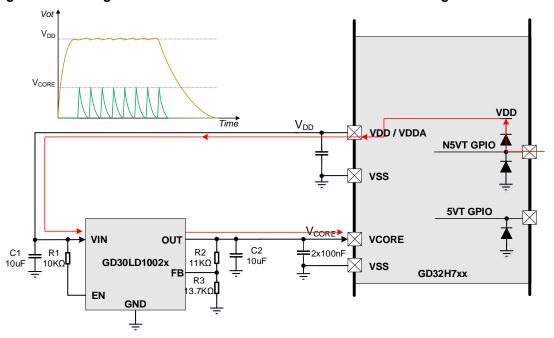

The circuit schematic is as shown in <u>Figure 4-1</u>. <u>Using LDO to supply power to VCORE</u> <u>schematic diagram</u>:

Figure 4-1. Using LDO to supply power to VCORE schematic diagram

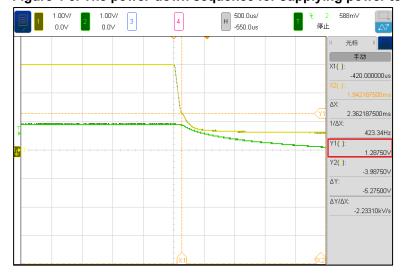

Powering VCORE with this chip, the power-up and power-down timing sequences are as shown in *Figure 4-2. The power-up sequence for supplying power to VCORE using LDO*, *Figure 4-3. The power-down sequence for supplying power to VCORE using LDO*, and it can be observed that the power-up and power-down timing sequences can meet the specified requirements.

Figure 4-2. The power-up sequence for supplying power to VCORE using LDO

Figure 4-3. The power-down sequence for supplying power to VCORE using LDO

Note: If the VDD power-up speed is too fast, it may also cause the power-up sequence to not meet the requirements.

### 4.2. The Impact of GPIO on Power Bypass Mode

The GPIO of GD32H7xx is divided into 5VT and N5VT, with one difference being that N5VT has pull-up protection diodes to VDD. For more details, you can refer to "AN092 GD32 MCU GPIO structure and precautions".

When using the power bypass mode, during the power-up and power-down stages of the MCU or during power loss, if the N5VT GPIO still has level driving, current may flow from the outside through the internal pull-up diodes to VDD, and then to the external LDO to generate VCORE voltage. If the driving current is insufficient or the voltage reached by leakage is at the critical value for LDO startup, it may cause the external LDO to not start stably, resulting in oscillation of its output VCORE voltage. As shown in *Figure 4-4. Leakage current in GPIO causes oscillation in VCORE voltage*

This is an unstable state. If at this time the VDD voltage is greater than the POR threshold, the chip will start up, but if the VCORE core voltage is unstable, it can lead to unpredictable risks. In many usage scenarios, the MCU GPIO periphery will use diode protection circuits, which can also cause such situations to occur.

Figure 4-4. Leakage current in GPIO causes oscillation in VCORE voltage

Considering this, it is important to avoid the situation where GPIO leakage to VDD occurs due to GPIO being driven by a level during the MCU's power-up and power-down stages or during power loss.

### 4.3. Optimization Schemes for Power Bypass Mode

For the above-mentioned leakage issue, it is required to always follow the Datasheet's specified maximum GPIO input voltage not exceeding VDD + 0.3 V and an input current of 0. If the related issues cannot be avoided under working conditions, the following solution options can be selected for optimized design.

#### 4.3.1. Use reset chip solution.

A reset chip can be added to the VDD terminal to ensure that when the voltage leaked to VDD is below the reset threshold, NRST can be pulled low directly to avoid malfunction. Additionally, it can also circumvent non-compliant power-up and power-down sequences, as shown in *Figure 4-5. Use a reset chip to prevent misoperation*. The reset chip should be chosen with an open-drain output to avoid affecting the MCU's own reset actions in other scenarios. The minimum operating voltage of the reset chip should be lower than the PDR, to prevent NRST from being pulled back up after the reset chip powers down during shut-off. The monitoring voltage is generally advisable to be 90% of VDD; for example, if VDD = 3.3 V, a reset chip of 3.08 V or 2.93 V can be selected.

Figure 4-5. Use a reset chip to prevent misoperation

# 5. Precautions for Using External Power Supplies

- 1. The input voltage range for  $V_{CORE}$  is 0.873 V to 0.955 V, so it should be ensured that the typical value is 0.9 V, and the power supply ripple should be below 50 mV. Even in harsher application scenarios, the power supply fluctuation range should also be ensured to be within 50 mV.

- It is recommended that the load capacity of external components should be greater than 600 mA, and in extreme environments, it should be considered to use no less than 800 mA. Moreover, the output voltage fluctuation range under different loads should also meet the aforementioned requirement of 50 mV.

- 3. The ESR effect of PCB traces and the IR drop with high current, when routing PCB traces, it is necessary to consider widening the trace width from the external power supply to the VCORE pin to reduce ESR, ensuring that the voltage at the chip's VCORE pin meets the amplitude and fluctuation requirements.

# 6. Revision history

Table 6-1. Revision history

| Revision No. | Description                      | Date         |

|--------------|----------------------------------|--------------|

| 1.0          | Initial Release                  | Dec.18, 2024 |

|              | 1. Add instructions for software |              |

|              | switching in Chapter 2.          |              |

|              | 2、Add an explanation in          |              |

| 4.4          | Chapter 3 about pulling          | Fab 27 2025  |

| 1.1          | PDR_ON up to VDD.                | Feb.27.2025  |

|              | 3. Add a description of power-   |              |

|              | up speed in Section 4.1          |              |

|              | summary.                         |              |

#### **Important Notice**

This document is the property of GigaDevice Semiconductor Inc. and its subsidiaries (the "Company"). This document, including any product of the Company described in this document (the "Product"), is owned by the Company under the intellectual property laws and treaties of the People's Republic of China and other jurisdictions worldwide. The Company reserves all rights under such laws and treaties and does not grant any license under its patents, copyrights, trademarks, or other intellectual property rights. The names and brands of third party referred thereto (if any) are the property of their respective owner and referred to for identification purposes only.

The Company makes no warranty of any kind, express or implied, with regard to this document or any Product, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. The Company does not assume any liability arising out of the application or use of any Product described in this document. Any information provided in this document is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Except for customized products which has been expressly identified in the applicable agreement, the Products are designed, developed, and/or manufactured for ordinary business, industrial, personal, and/or household applications only. The Products are not designed, intended, or authorized for use as components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, atomic energy control instruments, combustion control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, life-support devices or systems, other medical devices or systems (including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the failure of the device or Product could cause personal injury, death, property or environmental damage ("Unintended Uses"). Customers shall take any and all actions to ensure using and selling the Products in accordance with the applicable laws and regulations. The Company is not liable, in whole or in part, and customers shall and hereby do release the Company as well as it's suppliers and/or distributors from any claim, damage, or other liability arising from or related to all Unintended Uses of the Products. Customers shall indemnify and hold the Company as well as it's suppliers and/or distributors harmless from and against all claims, costs, damages, and other liabilities, including claims for personal injury or death, arising from or related to any Unintended Uses of the Products.

Information in this document is provided solely in connection with the Products. The Company reserves the right to make changes, corrections, modifications or improvements to this document and Products and services described herein at any time, without notice.

© 2025 GigaDevice - All rights reserved