## GigaDevice Semiconductor Inc.

## GD32H73x/H75x 芯片使用限制

勘误手册

1.7 版本

(2025年11月)

# 目录

| 目录                      |                                                    | 2             |

|-------------------------|----------------------------------------------------|---------------|

| 图索引.                    |                                                    | 4             |

| 表索引.                    |                                                    | 5             |

| 1. 前                    | ]言                                                 | 6             |

| 1.1.                    | 芯片版本定义                                             | 6             |

| 1.2.                    | 芯片使用限制总览                                           | 6             |

| 2. 芯                    | 5片使用限制描述                                           | 9             |

|                         | SYSTEM                                             |               |

| 2.1.1<br>2.1.2<br>2.1.3 | . 当 SysTick 使用外部时钟源时,SysTick 时钟为系统时钟(CK_SYS)的 2 分频 | 9<br>9<br>性导致 |

| <b>2.2.</b> 2.2.1       | <b>FMC</b>                                         | _             |

| <b>2.3.</b> 2.3.1 2.3.2 |                                                    | 10            |

| <b>2.4.</b> 2.4.1 2.4.2 |                                                    | 11<br>电压,     |

| <b>2.5.</b> 2.5.1       | <b>TRNG</b>                                        |               |

| <b>2.6.</b> 2.6.1 2.6.2 |                                                    | 12            |

| <b>2.7.</b> 2.7.1       | <b>ADC</b>                                         |               |

| <b>2.8.</b> 2.8.1 2.8.2 |                                                    | 13            |

| <b>2.9.</b> 2.9.1       | TIMER         TIMER 中断存在误触发的风险                     |               |

| 2.10.                   | USART                                              | 14            |

## GD32H73x/H75x 芯片使用限制

| 2.10.1.  | 当使能 USART FIFO 功能时,USART 无法发送帧的最后一个字节                      | 14  |

|----------|------------------------------------------------------------|-----|

| 2.10.2.  | 当同时使能 USART 的 FIFO 和 DMA 功能时,DMA 只能传输一次数据                  | 14  |

| 2.10.3.  | LIN 模式下会发生数据采样错误                                           | 14  |

| 2.10.4.  | 在静默模式下,非唤醒帧引起的奇偶校验错会导致 PERR 置位                             | 15  |

| 2.11.    | I2S                                                        | 15  |

| 2.11.1.  | 当使用 I2S1 进行通信且 GPIO 和 I2S1 配置处于特殊组合时,可能会导致 I2S1_CK 和 I2S1_ | _ws |

|          | 引脚持续输出信号                                                   | 15  |

| 2.12.    | OSPI                                                       | 15  |

| 2.12.1.  | 当 OSPI 使用间接写模式时,中断和 DMA 功能无效                               | 15  |

| 2.12.2.  |                                                            |     |

| 2.12.3.  | 当 OSPI 运行时钟大于 100MHz 时,在状态轮询模式下读取外部存储器状态标志异常               | 16  |

| 2.13.    | EXMC                                                       | 16  |

| 2.13.1.  |                                                            |     |

| 2.13.2.  | 在访问 SDRAM 期间,可能会出现总线卡住的情况                                  | 17  |

| 2.13.3.  | 不支持非对齐地址访问                                                 | 17  |

| 2.14.    | LPDTS                                                      | 17  |

| 2.14.1.  | 禁用 LPDTS 后,温度传感器 ready 标志位无法清除                             | 17  |

| 2.15.    | CAN                                                        | 17  |

| 2.15.1.  |                                                            |     |

| 2.15.2.  | CAN 发送节点执行了不必要的自动校准                                        | 18  |

| 2.15.3.  | CAN 外设在未使用 HXTAL 时无法工作                                     | 18  |

| 2.15.4.  | 在接收邮箱处理过程中,CAN RAM 区域可能会被篡改                                | 18  |

| 2.15.5.  | 在总线离线恢复后,发送错误计数未自动清零                                       | 19  |

| 2.15.6.  | 邮箱数据未及时读走,可能会导致当前帧和下一帧数据读取错误                               | 19  |

| 2.15.7.  | 当 CAN 运行时钟频率低于 CK_APB2 且 DLC 段发生错误时,会导致接收到错误的帧 ID          | 20  |

| 2.16.    | USBHS                                                      | 20  |

| 2.16.1.  | USBHS OTG 灵敏度问题                                            | 20  |

| 2.17.    | Core                                                       | 20  |

| 14ct - 4 | k Et th                                                    | 24  |

## 图索引

| 圂   | 1_1  | GD32H73x/H75x     | 的芯片修订版本 |                                        | ß |

|-----|------|-------------------|---------|----------------------------------------|---|

| 131 | 1-1. | ODJZIII JAIIII JA | 叫心川廖阳枫牛 | ······································ | • |

# 表索引

| 表 1-1. | 适用产品    |

|--------|---------|

| 表 1-2. | 芯片使用限制( |

## 1. 前言

该文档适用于 GD32H73x/H75x 产品, 具体参考 <u>表 1-1. 适用产品</u>。该文档提供了在使用 GD32 MCU 过程中需要注意的技术细节,以及相关问题的解决方案。

表 1-1. 适用产品

| 类型  | 产品系列          |  |

|-----|---------------|--|

|     | GD32H737xx 系列 |  |

| MCU | GD32H757xx 系列 |  |

|     | GD32H759xx 系列 |  |

## 1.1. 芯片版本定义

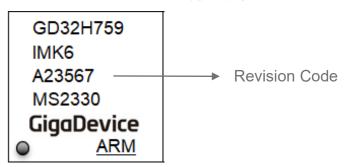

可通过芯片丝印上的标记来确定当前芯片的版本。丝印上第 3 行的第 1 个编码表示芯片当前版本,如*图 1-1. GD32H73x/H75x 的芯片修订版本*所示。

图 1-1. GD32H73x/H75x 的芯片修订版本

## 1.2. 芯片使用限制总览

GD32H73x/H75x 芯片使用限制参考<u>表 1-2. 芯片使用限制</u>。关于芯片使用限制的更多详细信息请参考第 2 章。

表 1-2. 芯片使用限制

|        | 使用限制                                                        |   | 解决方案 |  |

|--------|-------------------------------------------------------------|---|------|--|

| 模块     |                                                             |   | 修订版本 |  |

|        |                                                             | Α | С    |  |

|        | 当 SysTick 使用外部时钟源时,SysTick 时钟为系统时钟<br>(CK_SYS)的2分频          | Y |      |  |

| SYSTEM | 非法的地址访问会导致 ECC 错误                                           | Υ |      |  |

|        | 系统运行在高主频且中断向量表和中断处理代码均放置在 ITCM<br>中时,高频中断会概率性导致 ITCM ECC 误报 | Y | Y    |  |

| FMC    | 移除保护的整片擦除功能无法禁用                                             | N |      |  |

| PMU    | LQFP 封装的芯片使用 SMPS 模式时,存在芯片损坏风险                              | Y |      |  |

|       |                                            | 解决方案 |      |

|-------|--------------------------------------------|------|------|

| 模块    | 使用限制                                       | 修订版本 | 修订版本 |

|       |                                            | Α    | С    |

|       | 未使用 SMPS 时,不能将 VDDSMPS 连接到低电平              | Y    |      |

|       | MCU 进入待机模式时,PXY 引脚将连接到 PXY_C 引脚            | Y    |      |

| GPIO  | 当 VDD 和 VDDA 掉电后,如果继续向 GPIO(除 PA9 / PA10 / |      |      |

|       | PB12 / PB13 外)注入电压,可能导致芯片 GPIO 出现过流风险      | Y    | Y    |

| TRNG  | LFSR 算法失效                                  | Υ    |      |

| DDC   | 使用低功耗调试功能时,SWD 和 JTAG 调试功能失效               | N    |      |

| DBG   | 当 PA15 为低电平时,SWD 连接失败                      | Y    |      |

| ADC   | 在 14 位 ADC 中同时使用过采样时,模拟看门狗阈值比较失败           | Y    |      |

|       | 使用 RTC 参考时钟检测功能时,PB13 / PB15 将被配置为输入浮      |      |      |

| RTC   | <i>空模式</i>                                 | Y    |      |

|       | 备份域中的电压或温度变化无法触发侵入检测功能                     | N    |      |

| TIMER | TIMER 中断存在误触发的风险                           | Y    | Y    |

|       | 当使能 USART FIFO 功能时,USART 无法发送帧的最后一个字       |      |      |

|       | #                                          | Y    |      |

|       | 当同时使能 USART 的 FIFO 和 DMA 功能时,DMA 只能传输一次    |      |      |

| USART | <b>数据</b>                                  | Y    |      |

|       | LIN 模式下会发生数据采样错误                           | Y    | Y    |

|       | 在静默模式下,非唤醒帧引起的奇偶校验错会导致 PERR 置位             | Y    | Y    |

| 100   | 当使用 I2S1 进行通信且 GPIO 和 I2S1 配置处于特殊组合时,可     | V    | V    |

| I2S   | 能会导致 I2S1_CK 和 I2S1_WS 引脚持续输出信号            | Y    | Y    |

|       | 当 OSPI 使用间接写模式时,中断和 DMA 功能无效               | Y    |      |

| OSPI  | 当 OSPI 仅发送数据段时,第一个时钟会丢失                    | Y    | Y    |

| USPI  | 当 OSPI 运行时钟大于 100MHz 时,在状态轮询模式下读取外部        | V    | V    |

|       | 存储器状态标志异常                                  | Y    | Y    |

|       | SDRAM 控制器的自动刷新功能受到其他 EXMC 控制器的影响           | Y    |      |

| EXMC  | 在访问 SDRAM 期间,可能会出现总线卡住的情况                  | Υ    | Υ    |

|       | 不支持非对齐地址访问                                 | Y    | Y    |

| LPDTS | 禁用 LPDTS 后,温度传感器 ready 标志位无法清除             | Y    |      |

|       | 发送邮箱在退出未激活模式时可能会发生传输失败                     | Υ    |      |

|       | CAN 发送节点执行了不必要的自动校准                        | Y    |      |

|       | CAN 外设在未使用 HXTAL 时无法工作                     | Y    |      |

| CAN   | 在接收邮箱处理过程中,CAN RAM 区域可能会被篡改                | Y    | Y    |

| CAN   | 在总线离线恢复后,发送错误计数未自动清零                       | Y    | Υ    |

|       | 邮箱数据未及时读走,可能会导致当前帧和下一帧数据读取错误               | Y    | Y    |

|       | 当 CAN 运行时钟频率低于 CK_APB2 且 DLC 段发生错误时,会      | V    | V    |

|       | 导致接收到错误的帧 ID                               | Y    | Y    |

| USBHS | USBHS OTG 灵敏度问题                            | Y    |      |

## 注意:

Y = 存在使用限制且存在解决方案

N = 存在使用限制但不存在解决方案

'--' = 使用限制已修复

## 2. 芯片使用限制描述

## 2.1. SYSTEM

#### 描述与影响

当 SysTick 使用外部时钟源时, SysTick 时钟为系统时钟(CK\_SYS)的 2 分频而不是 8 分频。

## 解决方案

当 SysTick 使用外部时钟源时,使用 CK\_SYS / 2 去计算 SysTick 时间。

## 2.1.2. 非法的地址访问会导致 ECC 错误

## 描述与影响

当访问非法地址时, CPU 将产生 ECC 错误。

## 解决方案

使用以下解决方案之一:

- 1) 避免访问非法地址。

- 2) 在访问非法地址后,应使用软件去处理 ECC 错误。

# 2.1.3. 系统运行在高主频且中断向量表和中断处理代码均放置在 ITCM 中时,高频中断会概率性导致 ITCM ECC 误报

## 描述与影响

当系统时钟配置为高频(如 600MHz),AXI/AHB 时钟配置为系统时钟的二分频且 TCM 插入等待周期时(TCM\_WAITSTATE = 1),如果将中断向量表和中断处理代码都放置在 ITCM 中,若有高频中断产生,会概率性导致 ITCM ECC 误报。

注意: 当系统时钟高于 350MHz 时, TCM 需要插入等待周期。

## 解决方案

使用以下解决方案之一:

- 1) 将中断向量表放置在 AXISRAM 中。

- 2) 避免将中断向量表和中断处理代码都放在同一块 TCM 中。例如,可以将中断向量表放置在 DTCM 中,中断处理代码放在 ITCM 中。

3) 采用降频方案。避免 TCM\_WAITSTATE = 1 和 AXI/AHB 时钟配置为系统时钟的二分频同时满足。如系统时钟和 AXI/AHB 时钟均配置为 300MHz。

## 2.2. FMC

## 2.2.1. 移除保护的整片擦除功能无法禁用

#### 描述与影响

移除保护的整片擦除操作仅在满足以下条件时才会执行移除保护功能:

- 1. 如果存在安全用户区域,则需置位 FMC\_SCRADDR\_MD 寄存器中的 SCR\_EREN 位, 并 通 过 在 FMC\_SCRADDR\_EFT 寄 存 器 中 设 置 SCR\_AREA\_END < SCR AREA START,确保安全用户区域的结束地址小于起始地址。

- 2. 如果存在任何擦除/编程保护的扇区,则需在 FMC\_WP\_MDF 寄存器中设置所有 WP(写保护)位。

- 3. 如果必要,需解锁 FMC CTL 寄存器。

否则,移除保护的整片擦除功能将无法禁用。有关移除保护的整片擦除的详细信息,请参考用户手册第 3.3.5 小节。

## 解决方案

无规避方案。

## 2.3. PMU

## 2.3.1. LQFP 封装的芯片使用 SMPS 模式时,存在芯片损坏风险

#### 描述与影响

在 LQFP 封装中,当芯片工作在 SMPS 模式且结温(Tj)超过 125°C 时,会存在因漏电而导致芯片损坏的风险。

注意: 此限制适用于 LQFP176 封装。

## 解决方案

避免在 LQFP 封装芯片中使用 SMPS 模式。

## 2.3.2. 未使用 SMPS 时,不能将 VDDSMPS 连接到低电平

## 描述与影响

未使用 SMPS 时, VDDSMPS 不能连接到低电平。

注意: 此限制适用于 LQFP176 和 BGA176 封装。

#### 解决方案

在未使用 SMPS 模式时,将 VDDSMPS 引脚连接到高电平或保持浮空。

## 2.4. **GPIO**

## 2.4.1. MCU 进入待机模式时,PXY 引脚将连接到 PXY\_C 引脚

## 描述与影响

当 MCU 进入待机模式时,PXY 引脚将连接到 PXY\_C 引脚,包括 PA0 / PA0\_C、PA1 / PA1\_C、PC2 / PC2\_C 和 PC3 / PC3\_C。

## 解决方案

根据应用场景评估影响,例如在待机模式下使用 PAO 作为唤醒引脚。

# 2.4.2. 当 VDD 和 VDDA 掉电后,如果继续向 GPIO(除 PA9 / PA10 / PB12 / PB13外)注入电压,可能导致芯片 GPIO 出现过流风险

## 描述与影响

当芯片的 VDD 和 VDDA 掉电后,如果继续向 GPIO(除 PA9 / PA10 / PB12 / PB13 外)外部注入电压(Vin),由于 GPIO 的 ESD 保护电路,外部注入的电压可能会泄漏到 VDD,形成 Vin-0.7V 的电压。如果 Vin-0.7V 接近 POR(1.6V),可能会满足芯片的 POR 条件。然而,由于 GPIO 的过流能力有限,这可能导致系统发生重复的 POR/PDR 事件,从而引发系统不可预测的风险。

## 解决方案

在系统设计中,应在芯片的 VDD 和 NRST 之间外接一个欠压复位芯片,以确保当 GPIO 泄漏到 VDD 的电压低于欠压复位芯片的阈值电压时,可以直接拉低 NRST 以避免错误操作。具体解决方案可参考《AN225 GD32H7xx 电源旁路模式使用指南》。

## 2.5. TRNG

## 2.5.1. LFSR 算法失效

## 描述与影响

用于生成随机数的 LFSR(线性反馈移位寄存器)算法无法正常工作。

## 解决方案

不使用 LFSR 算法,改用 NIST (美国国家标准与技术研究院)算法。

## 2.6. DBG

## 2.6.1. 使用低功耗调试功能时, SWD 和 JTAG 调试功能失效

## 描述与影响

当使用低功耗调试功能(置位 STB\_HOLD/DSLP\_HOLD/SLP\_HOLD)时,调试功能将无法正常工作。

## 解决方案

避免使用低功耗调试功能。

## 2.6.2. 当 PA15 为低电平时, SWD 连接失败

## 描述与影响

上电后,如果 PA15 的电平为低电平,SWD 连接将失败。

## 解决方案

使用以下解决方案之一:

- 1) 在使用 SWD 调试时,不要将 PA15 驱动为低电平。

- 2) 不要将 PA15 配置为 AF0 功能。

## 2.7. ADC

## 2.7.1. 在 14 位 ADC 中同时使用过采样时,模拟看门狗阈值比较失败

#### 描述与影响

当在 14 位 ADC(ADC0/ADC1)中启用过采样功能时,模拟看门狗功能将失效,因为它不会将累积和与低阈值进行比较。

## 解决方案

不要在 14 位 ADC 中同时使用模拟看门狗功能和过采样功能。

## 2.8. RTC

## 2.8.1. 使用 RTC 参考时钟检测功能时, PB13 / PB15 将被配置为输入浮空模式

## 描述与影响

当使用 RTC 参考时钟检测功能(通过设置 RTC\_CTL 寄存器中的 REFEN 位)时, PB13/PB15 引脚将被设置为输入浮空模式。

## 解决方案

使用以下解决方案之一:

- 1) 不使用 RTC 参考时钟检测功能。

- 2) 在使用 RTC 参考时钟检测功能时,将 PB13 / PB15 设置为输入浮空模式。

## 2.8.2. 备份域中的电压或温度变化无法触发侵入检测功能

## 描述与影响

当由于 VDD 掉电导致备份域供电为 VBAT 时,电压和温度变化无法触发侵入检测功能。

### 解决方案

无规避方案。

## **2.9.** TIMER

## 2.9.1. TIMER 中断存在误触发的风险

## 描述与影响

当启用 TIMER 中断且 MCU 以高频率运行时,由于代码执行速度较快且清除中断标志需要一定的时间,可能导致无法及时清除相应的 TIMER 中断标志,从而存在重复进入 TIMER 中断的风险。

## 解决方案

在 TIMER 中断处理函数的开始位置清除相应的 TIMER 中断标志,并在退出中断前保持至少 20 个指令周期。

## 2.10. **USART**

## 2.10.1. 当使能 USART FIFO 功能时,USART 无法发送帧的最后一个字节

## 描述与影响

当启用 USART FIFO 功能时,USART 无法发送帧的最后一个字节。例如,在发送十个字符 "0123456789"时,字符"9"将不会被发送。

## 解决方案

在发送帧的末尾填充一个无效字节,例如在"0123456789\n"中添加"\n",并确保正确传输,需在每次数据发送前执行以下操作:

- 1) 禁用 FIFO

- 2) 禁用 USART

- 3) 执行数据刷新请求(设置 TXFCMD 位)

- 4) 启用 FIFO

- 5) 启用 USART

## 2.10.2. 当同时使能 USART 的 FIFO 和 DMA 功能时,DMA 只能传输一次数据

## 描述与影响

当同时使能 USART 的 FIFO 和 DMA 功能时, DMA 只能传输一次数据。

## 解决方案

使用以下解决方案之一:

- 1) 仅使用 USART DMA,不要使用 USART FIFO。

- 2) 仅使用 USART FIFO,不要使用 USART DMA。

## 2.10.3. LIN 模式下会发生数据采样错误

## 描述与影响

当 USART 作为接收器处于 LIN 模式时,由于在接收断开帧之前启用了自动波特率检测功能,会发生数据采样错误。

## 解决方案

- 1) 在接收断开帧之前禁用自动波特率检测功能。

- 2) 在置位 LIN 断开帧检测标志(LBDF)后启用自动波特率检测功能。

## 2.10.4. 在静默模式下,非唤醒帧引起的奇偶校验错会导致 PERR 置位

## 描述与影响

在静默模式下,由非唤醒帧引起的奇偶校验错误会导致奇偶校验错误(USART\_STAT 寄存器中的 PERR 位被设置),即使唤醒帧中没有发现奇偶校验错误。

## 解决方案

软件忽略在这种情况下生成的奇偶校验错误标志。

## 2.11. I2S

# 2.11.1. 当使用 I2S1 进行通信且 GPIO 和 I2S1 配置处于特殊组合时,可能会导致 I2S1\_CK 和 I2S1\_WS 引脚持续输出信号

## 描述与影响

当使用 I2S1 进行通信,且 GPIO 和 I2S1 配置为特殊组合时,I2S1\_CK 和 I2S1\_WS 引脚将概率性地连续输出信号。具体配置及现象如下:

| GPIO 配置            | I2S1 配置       | 现象                     |

|--------------------|---------------|------------------------|

| GPIO 能且            | 1231 阻止       | <b>火</b> 豕             |

| GPIO_PUPD_PULLDOWN | I2S_CKPL_HIGH | I2S1_CK 和 I2S1_WS 连续发波 |

| GPIO_PUPD_NONE     | I2S_CKPL_HIGH | I2S1_CK 和 I2S1_WS 连续发波 |

| GPIO_PUPD_PULLUP   | I2S_CKPL_HIGH | I2S1 工作正常              |

| GPIO_PUPD_PULLDOWN | I2S_CKPL_LOW  | I2S1 工作正常              |

| GPIO_PUPD_PULLUP   | I2S_CKPL_LOW  | I2S1 工作正常              |

| GPIO_PUPD_NONE     | I2S_CKPL_LOW  | I2S1 工作正常              |

## 解决方案

GPIO 和 I2S1 的正确配置请参考上述。

## 2.12. **OSPI**

## 2.12.1. 当 OSPI 使用间接写模式时,中断和 DMA 功能无效

## 描述与影响

当使用 OSPI 间接写模式时,中断和 DMA 功能无效,因为 FIFO 阈值标志 (FT) 无法被置位。

## 解决方案

使用状态轮询模式代替间接写模式。

## 2.12.2. 当 OSPI 仅发送数据段时,第一个时钟会丢失

#### 描述与影响

当 OSPI 仅发送数据段时,第一个时钟会丢失,从而导致第一个数据丢失。

#### 解决方案

将第一个数据作为命令发送。

# 2.12.3. 当 OSPI 运行时钟大于 100MHz 时,在状态轮询模式下读取外部存储器状态标志异常

## 描述与影响

当 OSPI 运行时钟大于 100MHz 时,由于硬件连续轮询间隔不足,外部存储器可能未准备好,随后 OSPI 将执行后续操作,从而导致异常。

#### 解决方案

在每次轮询存储器状态之前添加硬件延迟 (例如 20ms 延迟)。

## 2.13. **EXMC**

## 2.13.1. SDRAM 控制器的自动刷新功能受到其他 EXMC 控制器的影响

## 描述与影响

SDRAM 控制器的自动刷新功能受到其他 EXMC 控制器的影响。当 SDRAM 控制器执行自动刷新命令时,如果 SDRAM 存储区处于激活状态,则需要生成预充电命令,并要求 EXMC\_A10端口为 1。而此时 EXMC\_A10端口被其他 EXMC 控制器使用,导致 SDRAM 自动刷新命令执行异常,从而引发 SDRAM 数据错误。

### 解决方案

步骤 1: 在 EXMC 初始化后, 使 EXMC SDRAM 控制器与其他控制器同时工作。

/\* code example \*/

REG32(EXMC + 0x184U) = 0x9EF02310U;

EXMC\_SDRSCTL |= BIT(9);

## 步骤 2:

方法 1: 当 SDRAM 控制器选择操作的 BANK 地址时,引脚输出不使用 AF 功能,而是通过 GPIO 直接驱动 BANK 地址来访问对应的 BANK。

方法 2: 在 EXMC 操作 NAND FLASH 之前,添加 SDRAM 的全局预充电指令,使 SDRAM 的自刷新操作不依赖于原来的预充电指令,这样即使自刷新和 NAND 同时发生,也不会出现错误。

/\* code example \*/

REG32(0xA0000150U) = (uint32\_t)0x00000012U; while(0x000000000 != (REG32(0xA0000158U) & 0x00000020)) {

## 2.13.2. 在访问 SDRAM 期间,可能会出现总线卡住的情况

## 描述与影响

在访问 SDRAM 时,如果 SDRAM 数据位宽为 32 位,总线发送两个 8 位或两个 16 位访问,然后发送一个 64 位访问,如果 64 位访问的数据恰好由之前的两个 8 位或 16 位访问组成,则总线可能会卡住。

## 解决方案

使用以下解决方案之一:

- 1) 禁用 SDRAM 的突发访问(清除 EXMC\_SDCTL0/1 寄存器的 BRSTRD 位)

- 2) 使能 CPU 缓存功能

## 2.13.3. 不支持非对齐地址访问

#### 描述与影响

总线不支持对 SDRAM 的非对齐地址访问。

## 解决方案

在访问 SDRAM 之前启用 CPU 的缓存功能。

## 2.14. LPDTS

## 2.14.1. 禁用 LPDTS 后,温度传感器 ready 标志位无法清除

## 描述与影响

关闭 LPDTS(低功耗数字温度传感器)后,温度传感器就绪标志(TSRF)将无法清除。

#### 解决方案

在使能 LPDTS 之前, 先复位 LPDTS 外设。

## 2.15. CAN

## 2.15.1. 发送邮箱在退出未激活模式时可能会发生传输失败

## 描述与影响

如果邮箱在未激活模式下被配置为发送邮箱(Tx mailbox),退出未激活模式后可能由于缺少内部触发而无法发送。

#### 解决方案

使用以下解决方案之一:

- 1) 使用另一个节点发送一次帧。

- 2) 软件写入一个无效邮箱。

## 2.15.2. CAN 发送节点执行了不必要的自动校准

## 描述与影响

当延迟(从 TX 到 RX 回读  $+ 2 * CK_CAN$ )超过一个 Tq 时间时,CAN 会自动执行校准,导致发送的显性电平延长并出现错误。

#### 解决方案

使用 GD32 MCU CAN 传输软件解决方案,参考"AN222 GD32A5x3 CAN 位时间问题的软件规避"。

## 2.15.3. CAN 外设在未使用 HXTAL 时无法工作

#### 描述与影响

当 HXTAL 时钟未启用时, CAN 外设无法工作。

#### 解决方案

打开 HXTAL 时钟并等待其稳定后再配置 CAN 外设时钟源,然后根据需要关闭 HXTAL 时钟。

## 2.15.4. 在接收邮箱处理过程中, CAN RAM 区域可能会被篡改

## 描述与影响

如果在接收邮箱处理例程中未执行全局邮箱解锁操作(由于软件操作错误), CAN RAM 区域有一定概率会被篡改,从而导致数据传输和接收异常。

## 解决方案

在每次数据传输之前,等待 CAN\_STAT 寄存器中的发送完成标志置位,而不是通过发送邮箱的 CODE 段值进行判断。参考代码如下:

```

Flagstatus can_tx_status = RESET;

{

if(((RESET == can_tx_state) || (SET == can_flag_get(CAN1, CAN_FLAG_MB1))){

can_tx_state = SET;

can_flag_clear(CAN1, CAN_FLAG_MB1);

/* transmit message */

```

```

can_mailbox_config(CAN1, 1, &transmit_message);

/* user code */

}

```

## 2.15.5. 在总线离线恢复后,发送错误计数未自动清零

## 描述与影响

在总线离线恢复后,发送错误计数(TECNT)未被硬件自动清零。

## 解决方案

在总线关闭恢复后,使用软件方法清除发送错误计数(TECNT)。以 CAN1 为例,参考代码如下:

## 2.15.6. 邮箱数据未及时读走,可能会导致当前帧和下一帧数据读取错误

#### 描述与影响

在处理邮箱接收时,如果在读取当前帧数据时,一个新的 CAN 帧(下一帧)被移入接收邮箱,可能导致当前帧和下一帧数据读取错误。

注意: 仅影响当前帧和下一帧。

## 解决方案

使用以下解决方案之一:

- **1)** 使用邮箱接收中断并将其配置为最高优先级。当接收邮箱中断发生时,及时读取并处理邮箱数据(在下一帧结束之前)。

- 2) 使用 CAN FIFO 接收代替邮箱接收。

- 3) 通过置位 RPFQEN 使能邮箱队列,并将邮箱接收中断设置为最高优先级。

# 2.15.7. 当 CAN 运行时钟频率低于 CK\_APB2 且 DLC 段发生错误时,会导致接收到错误的帧 ID

## 描述与影响

当 CAN 运行时钟频率低于 CK\_APB2 时,如果 CAN 总线上的外部干扰导致在接收帧时,DLC 段检测到错误并发送错误帧,则会导致后续帧接收到错误帧 ID (即使该错误帧 ID 已被 CAN 滤波器过滤)。

## 解决方案

使用以下解决方案之一:

1) 软件将 CAN 时钟源配置为 CK APB2。以 CAN1 为例,参考代码如下:

```

{

/* configure the CAN1 clock source as CK_APB2 */

rcu_can_clock_config(IDX_CAN1, RCU_CANSRC_APB2);

}

```

- 2) 软件检查帧 ID (适用于 CAN 运行时钟频率低于 CK\_APB2 的情况)。当 CAN 邮箱接收到 非目标帧 ID 且发生错误时,软件需要重新配置 CAN 接收邮箱参数。具体配置步骤如下:

- a) 进入未激活模式

- b) 重新配置接收邮箱参数

- c) 进入正常模式

## 2.16. USBHS

## 2.16.1. USBHS OTG 灵敏度问题

#### 描述与影响

USBHS OTG 可以正常工作,但灵敏度测试不通过。

## 解决方案

通过配置 USBHS 内部对应的预留寄存器可以避免上述问题。

## 2.17. Core

关于 Cortex-M7 的限制,请参考"Cortex-M7 (AT610) and Cortex-M7 with FPU (AT611) Software Developer Errata Notice"。该文档可在 ARM 官方网站下载。

## 3. 版本历史

表 3-1. 版本历史

| 版本号. | 说明                                            | 日期              |

|------|-----------------------------------------------|-----------------|

| 1.0  | 首次发布                                          | 2023年9月12日      |

| 1.1  | 更新内容说明                                        | 2023年9月26日      |

| 1.2  | 1. 添加 C 版芯片使用限制                               | 2024年4月20日      |

| 1.2  | 2. 添加 USART / OSPI / EXMC 外设限制                | 2024 平 4 月 20 日 |

|      | 1. 更新 EXMC 限制描述及解决方案,参考                       |                 |

|      | SDRAM 控制器的自动刷新功能受到其他                          |                 |

|      | EXMC 控制器的影响                                   |                 |

|      | 2. 添加限制,参考 <i>TIMER 中断存在误触发的风</i>             |                 |

| 1.3  | <u> </u>                                      | 2024年8月5日       |

|      | 3. 添加限制,参考 <u>在接收邮箱处理过程中,CAN</u>              |                 |

|      | RAM 区域可能会被篡改                                  |                 |

|      | 4. 更新 CAN 限制解决方案,参考 <i>CAN 发送节点</i>           |                 |

|      | <u>执行了不必要的自动校准</u>                            |                 |

|      | 1. 更新 PMU 限制描述,参考 <i>LQFP 對裝的芯片</i>           |                 |

| 1.4  | <u>使用 SMPS 模式时,存在芯片损坏风险</u>                   | 2024年9月1日       |

| 1.4  | 2. 更新 TIMER 限制描述,参考 <i>TIMER 中断存在</i>         | 2024 平 9 万 1 日  |

|      | <u>误触发的风险</u>                                 |                 |

|      | 1. 添加 CAN 限制,参考 <u>在总线离线恢复后,发</u>             |                 |

|      | <i>送错误计数未自动清零</i>                             |                 |

|      | 2. 添加 CAN 限制,参考 <i>邮<b>箱数据未及时读走,</b></i>      |                 |

| 1.5  | <u>可能会导致当前帧和下一帧数据读取错误</u>                     | 2024年12月15日     |

|      | 3. 添加 CAN 限制,参考 <u>当 <b>CAN 运行时钟频率低</b></u>   |                 |

|      | <u>于 CK_APB2 且 DLC 段发生错误时,会导致</u>             |                 |

|      | <u>接收到错误的帧 ID</u>                             |                 |

|      | 添加 GPIO 限制,参考 <u>当 VDD 和 VDDA <b>掉电后,</b></u> |                 |

| 1.6  | <u>如果继续向 GPIO(除 PA9 / PA10 / PB12 / PB13</u>  | 2025年1月13日      |

|      | 外)注入电压,可能导致芯片 GPIO 出现过流风险                     |                 |

|      | 1. 添加 I2S 限制,参考当 <u>使用 I<b>2S1</b> 进行通信且</u>  |                 |

|      | GPIO 和 I2S1 配置处于特殊组合时,可能会导                    |                 |

|      | <u> </u>                                      |                 |

| 1.7  | 2. 添加 SYSTEM 限制,参考 <i>系统运行在高主频</i>            | 2025年11月15日     |

|      | 且中断向量表和中断处理代码均放置在 ITCM                        |                 |

|      | <u>中时,高频中断会概率性导致 ITCM ECC 误报</u>              |                 |

|      | 3. 添加 Core 限制参考                               |                 |

## **Important Notice**

This document is the property of GigaDevice Semiconductor Inc. and its subsidiaries (the "Company"). This document, including any product of the Company described in this document (the "Product"), is owned by the Company according to the laws of the People's Republic of China and other applicable laws. The Company reserves all rights under such laws and no Intellectual Property Rights are transferred (either wholly or partially) or licensed by the Company (either expressly or impliedly) herein. The names and brands of third party referred thereto (if any) are the property of their respective owner and referred to for identification purposes only.

To the maximum extent permitted by applicable law, the Company makes no representations or warranties of any kind, express or implied, with regard to the merchantability and the fitness for a particular purpose of the Product, nor does the Company assume any liability arising out of the application or use of any Product. Any information provided in this document is provided only for reference purposes. It is the sole responsibility of the user of this document to determine whether the Product is suitable and fit for its applications and products planned, and properly design, program, and test the functionality and safety of its applications and products planned using the Product. The Product is designed, developed, and/or manufactured for ordinary business, industrial, personal, and/or household applications only, and the Product is not designed or intended for use in (i) safety critical applications such as weapons systems, nuclear facilities, atomic energy controller, combustion controller, aeronautic or aerospace applications, traffic signal instruments, pollution control or hazardous substance management; (ii) life-support systems, other medical equipment or systems (including life support equipment and surgical implants); (iii) automotive applications or environments, including but not limited to applications for active and passive safety of automobiles (regardless of front market or aftermarket), for example, EPS, braking, ADAS (camera/fusion), EMS, TCU, BMS, BSG, TPMS, Airbag, Suspension, DMS, ICMS, Domain, ESC, DCDC, e-clutch, advanced-lighting, etc.. Automobile herein means a vehicle propelled by a selfcontained motor, engine or the like, such as, without limitation, cars, trucks, motorcycles, electric cars, and other transportation devices; and/or (iv) other uses where the failure of the device or the Product can reasonably be expected to result in personal injury, death, or severe property or environmental damage (collectively "Unintended Uses"). Customers shall take any and all actions to ensure the Product meets the applicable laws and regulations. The Company is not liable for, in whole or in part, and customers shall hereby release the Company as well as its suppliers and/or distributors from, any claim, damage, or other liability arising from or related to all Unintended Uses of the Product. Customers shall indemnify and hold the Company, and its officers, employees, subsidiaries, affiliates as well as its suppliers and/or distributors harmless from and against all claims, costs, damages, and other liabilities, including claims for personal injury or death, arising from or related to any Unintended Uses of the Product.

Information in this document is provided solely in connection with the Product. The Company reserves the right to make changes, corrections, modifications or improvements to this document and the Product described herein at any time without notice. The Company shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. Information in this document supersedes and replaces information previously supplied in any prior versions of this document.