### GigaDevice Semiconductor Inc.

### **Device limitations of GD32H73x/H75x**

### **Errata Sheet**

Revision 1.7

(Nov. 2025)

### **Table of Contents**

| Table    | e of | Contents2                                                                                                                                                                                                      | <u>)</u> |

|----------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| List     | of F | igures4                                                                                                                                                                                                        | ļ        |

| List     | of T | ables5                                                                                                                                                                                                         | 5        |

| 1.       | Int  | roduction                                                                                                                                                                                                      | 3        |

| 1.1.     | . F  | Revision identification6                                                                                                                                                                                       | 3        |

| 1.2.     | . 9  | Summary of device limitations                                                                                                                                                                                  | 3        |

| 2.       |      | scriptions of device limitations9                                                                                                                                                                              |          |

| <br>2.1. |      | SYSTEM                                                                                                                                                                                                         |          |

|          | 1.1. | SysTick is clocked with the system clock (CK_SYS) divided by 2 when using external clock source                                                                                                                | <        |

| 2.       | 1.2. | ECC error due to illegal address access                                                                                                                                                                        | )        |

| 2.       | 1.3. | When the system operates at high frequency and both the interrupt vector table and interrup handling code are placed in ITCM, high-frequency interrupts may probabilistically cause false ITCM ECC error alarm | Э        |

| 2.2.     | . F  | FMC                                                                                                                                                                                                            | )        |

| 2.       | 2.1. | Protection-removed mass erase function cannot be disabled                                                                                                                                                      | )        |

| 2.3.     | . F  | PMU 10                                                                                                                                                                                                         | )        |

| 2.       | 3.1. | Chip damage risk in SMPS mode of the LQFP package10                                                                                                                                                            |          |

| 2.       | 3.2. | VDDSMPS cannot be connected to a low level when not using SMPS1                                                                                                                                                | 1        |

| 2.4.     | . (  | SPIO 11                                                                                                                                                                                                        | l        |

|          | 4.1. | PXY pin connects to PXY_C pin in standby mode1                                                                                                                                                                 |          |

| 2.       | 4.2. | After VDD and VDDA are powered off, if voltage continues to be injected into GPIO (excep for PA9 / PA10 / PB12 / PB13), it may lead to an overcurrent risk in the chip's GPIO1                                 |          |

| 2.5.     | . 1  | TRNG 12                                                                                                                                                                                                        | <u>)</u> |

| 2.       | 5.1. | LFSR algorithm failure                                                                                                                                                                                         | 2        |

| 2.6.     | . [  | DBG 12                                                                                                                                                                                                         | <u> </u> |

| 2.       | 6.1. | SWD and JTAG debug function failure when using low power debug function 12                                                                                                                                     | 2        |

| 2.       | 6.2. | SWD connection fails when PA15 is low level                                                                                                                                                                    | 2        |

| 2.7.     |      | ADC13                                                                                                                                                                                                          | 3        |

| 2.       | 7.1. | The analog watchdog threshold comparison fails when used simultaneously with oversampling in a 14-bit ADC                                                                                                      |          |

| 2.8.     | . F  | RTC13                                                                                                                                                                                                          | 3        |

| 2.       | 8.1. | When using RTC reference clock detection function, PB13 / PB15 will be configured as inpu floating mode                                                                                                        |          |

| 2.       | 8.2. | Voltage or temperature changes in the backup domain cannot trigger the tamper function . 13                                                                                                                    | 3        |

| 2.9. T  | IMER                                                                                    | 14      |

|---------|-----------------------------------------------------------------------------------------|---------|

| 2.9.1.  | TIMER interrupt is at risk of triggering by mistake                                     | 14      |

| 2.10.   | USART                                                                                   | 14      |

| 2.10.1. |                                                                                         |         |

| 2.10.2. | •                                                                                       |         |

| 2.10.3. |                                                                                         |         |

| 2.10.4. | In mute mode, the parity error caused by non-wake frames will set PERR bit              | 15      |

| 2.11.   | 128                                                                                     | 16      |

| 2.11.1. | When I2S1 is used for communication and the GPIO and I2S1 configurations are in a       | special |

|         | combination, it will probabilistically cause the I2S1_CK and I2S1_WS pins to contin     | uously  |

|         | output signals                                                                          | 16      |

| 2.12.   | OSPI                                                                                    | 16      |

| 2.12.1. | Interrupt and DMA functions are invalid when OSPI is used in indirect write mode        | 16      |

| 2.12.2. | When OSPI sends only data segments, the first clock is lost                             | 17      |

| 2.12.3. | When OSPI running clock is greater than 100MHz, read external memory status flag ab     | normal  |

|         | in status polling mode                                                                  | 17      |

| 2.13.   | EXMC                                                                                    | 17      |

| 2.13.1. |                                                                                         |         |

| 2.13.2. | •                                                                                       |         |

| 2.13.3. | •                                                                                       |         |

| 2.14.   | LPDTS                                                                                   | 18      |

| 2.14.1. |                                                                                         |         |

| 2.15.   | CAN                                                                                     | 19      |

| 2.15.1. |                                                                                         |         |

| 2.15.2. | CAN transmit node performs unwanted automatic calibration                               | 19      |

| 2.15.3. | The CAN peripheral cannot function without using HXTAL                                  | 19      |

| 2.15.4. | CAN RAM area may be tampered in receiving mailbox processing                            | 20      |

| 2.15.5. | After Bus off recovery, transmit error count is not cleared automatically               | 20      |

| 2.15.6. | The mailbox data is not read in time may result in incorrect data reading for the curre | ent and |

|         | next frames                                                                             | 21      |

| 2.15.7. |                                                                                         |         |

|         | segment, which will lead to receiving an incorrect frame ID                             | 21      |

| 2.16.   | USBHS                                                                                   | 22      |

| 2.16.1. | USBHS OTG sensitivity problem                                                           | 22      |

| 2.17.   | Core                                                                                    | 22      |

| Roy     | vision history                                                                          | 23      |

## **List of Figures**

| gure 1-1. Device revision code of GD32H73x/H75x                                     | 6 |

|-------------------------------------------------------------------------------------|---|

| Jan 0 : 11 = 0 : 100 : 0 : 100 : 0 : 0 = 0 = 11 : 0 : 0 : 0 : 0 : 0 : 0 : 0 : 0 : 0 | _ |

### **List of Tables**

| Table 1-1. Applicable products | б  |

|--------------------------------|----|

| Table 1-2. Device limitations  | 6  |

| Table 3-1. Revision history    | 23 |

### 1. Introduction

This document applies to GD32H73x/H75x product series, as shown in <u>Table 1-1. Applicable</u> <u>products</u>. It offers technical guidance for using GD32MCU and provides workaround to current device limitations.

Table 1-1. Applicable products

| Туре | Part Numbers      |  |

|------|-------------------|--|

|      | GD32H737xx series |  |

| MCU  | GD32H757xx series |  |

|      | GD32H759xx series |  |

### 1.1. Revision identification

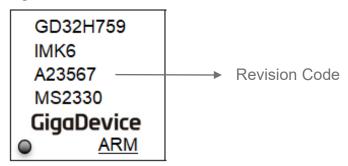

The device revision can be identified according to the mark on the top of the package. The 1st code on Line 3 of the mark is the product revision code, as shown in <u>Figure 1-1. Device</u> revision code of <u>GD32H73x/H75x</u>.

Figure 1-1. Device revision code of GD32H73x/H75x

### 1.2. Summary of device limitations

The device limitations of GD32H73X/H75X are shown in <u>Table 1-2. Device limitations</u>, please refer to Section 2 for more details.

Table 1-2. Device limitations

|        | Limitations                                                   |   | Workaround |  |

|--------|---------------------------------------------------------------|---|------------|--|

| Module |                                                               |   | Rev.       |  |

|        |                                                               |   | Code C     |  |

|        | SysTick is clocked with the system clock (CK_SYS) divided     | Y |            |  |

|        | by 2 when using external clock source                         |   |            |  |

| SYSTEM | ECC error due to illegal address access                       | Y |            |  |

|        | When the system operates at high frequency and both the       | Y | Υ          |  |

|        | interrupt vector table and interrupt handling code are placed | ſ | ſ          |  |

| In ITCM, high-frequency interrupts may probabilistically cause false ITCM ECC error   In ITCM, high-frequency interrupts may probabilistically cause false ITCM ECC error   In ITCM, high-frequency interrupts may probabilistically cause false ITCM ECC error   In ITCM, high-frequency interrupts may probabilistically cause false ITCM ECC error   In ITCM, high-frequency interrupts may probabilistically cause the I2ST_CK and I2ST_WS pins to continuously cause the I2ST_CK and I2ST_WS pins to controller is influenced by When OSPI running clock is greater than 100MHz, read external memory staus Iflag abnormal in stause polling mode   In ITCM, high-frequency in the bus may stuck during SDRAM access   Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                           | Limitations                                                                                                  |        | Workaround |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|--------------------------------------------------------------------------------------------------------------|--------|------------|--|

| in ITCM, high-frequency interrupts may probabilistically cause false ITCM ECC error  FMC Protection-removed mass erase function cannot be disabled N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Module                    |                                                                                                              |        | Rev.       |  |

| FMC Protection-removed mass erase function cannot be disabled N — Chip damage risk in SMPS mode of the LQFP package Y — SMPS SMPS PXY pin connects to PXY_C pin in standby mode Y — After VDD and VDDA are powered off, if voltage continues to be injected into GPIO (except for PA9 / PA10 / PB12 / PB13), it may lead to an overcurrent risk in the chip's GPIO PBG SWD and JTAG debug function failure when using low power debug function SWD connection fails when PA15 is low level Y — SWD connection fails when PA15 is low level Y — PB15 will be configured as input floating mode PB15 will be configured as input floating mode Y Uoltage or temperature changes in the backup domain cannot trigger the tamper function Y Y — When USART FIFO is enabled, the last byte of the frame cannot be transmitted When USART FIFO is enabled, DMA cannot transmit data Y — Data sample error occurs in LIN mode In mute mode, the parity error caused by non-wake frames will set PERR bit When USA is used for communication and the GPIO and I2S1 configurations are in a special combination, it will probabilistically cause the I2S1_CK and I2S1_WS pins to continuously output signals Interrupt and DMA functions are invalid when OSPI is used in indirect write mode  EXMC  Action PRESS PRE |                           |                                                                                                              | Code A | Code C     |  |

| Chip damage risk in SMPS mode of the LOFP package  VDDSMPS cannot be connected to a low level when not using SMPS  PXY pin connects to PXY_C pin in standby mode  After VDD and VDDA are powered off, if voltage continues to be injected into GPIO (except for PA9 / PA10 / PB12 / PB13), it may lead to an overcurrent risk in the chip's GPIO  TRNG  LFSR algorithm failure  SWD and JTAG debug function failure when using low power debug function  SWD connection fails when PA15 is low level  ADC  The analog watchdog threshold comparison fails when used simultaneously with oversampling in a 14-bit ADC  When using RTC reference clock detection function, PB13 / PB15 will be configured as input floating mode  Voltage or temperature changes in the backup domain cannot trigger the tamper function  TIMER ITIMER interrupt is at risk of triggering by mistake  When USART FIFO is enabled, the last byte of the frame cannot be transmitted  When USART FIFO is enabled, DMA cannot transmit data  When USART FIFO is enabled, DMA cannot transmit data  Pata sample error occurs in LIN mode  In mute mode, the parity error caused by non-wake frames will set PERR bit  When I2S1 is used for communication and the GPIO and I2S1 configurations are in a special combination, it will probabilistically cause the I2S1_CK and I2S1_WS pins to continuously output signals  Interrupt and DMA functions are invalid when OSPI is used in indirect write mode  When OSPI sends only data segments, the first clock is lost Y Y  When OSPI running clock is greater than 100MHz, read external memory status flag abnormal in status polling mode  Auto refresh function of SDRAM controller is influenced by other EXMC controller  The bus may stuck during SDRAM access  Y Y                                                                                                                                                                                                                                                                                                                          |                           |                                                                                                              |        |            |  |

| PMU VDDSMPS cannot be connected to a low level when not using SMPS  PXY pin connects to PXY_C pin in standby mode  After VDD and VDDA are powered off, if voltage continues to be injected into GPIO (except for PA9 / PA10 / PB12 / PB13), it may lead to an overcurrent risk in the chip's GPIO  TRNG LFSR algorithm failure  SWD and JTAG debug function failure when using low power debug function  SWD connection fails when PA15 is low level  ADC The analog watchdog threshold comparison fails when used simultaneously with oversampling in a 14-bit ADC  When using RTC reference clock detection function, PB13 / PB15 will be configured as input floating mode  Voltage or temperature changes in the backup domain cannot trigger the tamper function  TIMER TIMER interrupt is at risk of triggering by mistake  When USART FIFO is enabled, the last byte of the frame cannot be transmitted  When USART FIFO is enabled, DMA cannot transmit data  When USART FIFO is enabled, DMA cannot transmit data  Y  In mute mode, the parity error caused by non-wake frames will set PERR bit  When IZS1 is used for communication and the GPIO and IZS1 configurations are in a special combination, it will probabilistically cause the IZS1_CK and IZS1_WS pins to continuously output signals  Interrupt and DMA functions are invalid when OSPI is used in indirect write mode  OSPI When OSPI running clock is greater than 100MHz, read external memory status flag abnormal in status polling mode  Auto refresh function of SDRAM controller is influenced by other EXMC controller  The bus may stuck during SDRAM access  Y  Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | FMC                       | Protection-removed mass erase function cannot be disabled                                                    |        |            |  |

| SMPS  PXY pin connects to PXY_C pin in standby mode  After VDD and VDDA are powered off, if voltage continues to be injected into GPIO (except for PA9 / PA10 / PB12 / PB13), it may lead to an overcurrent risk in the chip's GPIO  TRNG  LFSR algorithm failure  SWD and JTAG debug function failure when using low power debug function  SWD connection fails when PA15 is low level  The analog watchdog threshold comparison fails when used simultaneously with oversampling in a 14-bit ADC  When using RTC reference clock detection function, PB13 / PB15 will be configured as input floating mode  Voltage or temperature changes in the backup domain cannot trigger the tamper function  TIMER  TIMER interrupt is at risk of triggering by mistake  When USART FIFO is enabled, the last byte of the frame cannot be transmitted  When USART FIFO is enabled, DMA cannot transmit data  Data sample error occurs in LIN mode  In mute mode, the parity error caused by non-wake frames will set PERR bit  When I2S1 is used for communication and the GPIO and I2S1 configurations are in a special combination, it will probabilistically cause the I2S1_CK and I2S1_WS pins to continuously output signals  Interrupt and DMA functions are invalid when OSPI is used in indirect write mode  When OSPI running clock is greater than 100MHz, read external memory status flag abnormal in status polling mode  Auto refresh function of SDRAM controller is influenced by other EXMC controller  The bus may stuck during SDRAM access  Y Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                           | Chip damage risk in SMPS mode of the LQFP package                                                            | Υ      |            |  |

| After VDD and VDDA are powered off, if voltage continues to be injected into GPIO (except for PA9 / PA10 / PB12 / PB13), it may lead to an overcurrent risk in the chip's GPIO  TRNG  LFSR algorithm failure  SWD and JTAG debug function failure when using low power debug function  SWD connection fails when PA15 is low level  The analog watchdog threshold comparison fails when used simultaneously with oversampling in a 14-bit ADC  When using RTC reference clock detection function, PB13 / PB15 will be configured as input floating mode  Voltage or temperature changes in the backup domain cannot trigger the tamper function  TIMER  TIMER interrupt is at risk of triggering by mistake  When USART FIFO is enabled, the last byte of the frame cannot be transmitted  When USART FIFO is enabled, DMA cannot transmit data  When USART FIFO is enabled, DMA cannot transmit data  Y  TIMER  When USART FIFO is enabled, DMA cannot transmit data  When USART sil is used for communication and the GPIO and I2S1 configurations are in a special combination, it will probabilistically cause the I2S1_CK and I2S1_WS pins to continuously output signals  Interrupt and DMA functions are invalid when OSPI is used in indirect write mode  OSPI  When OSPI sends only data segments, the first clock is lost  When OSPI running clock is greater than 100MHz, read external memory status flag abnormal in status polling mode  Auto refresh function of SDRAM controller is influenced by other EXMC controller  The bus may stuck during SDRAM access  Y  Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | PMU                       |                                                                                                              | Y      |            |  |

| be injected into GPIO (except for PA9 / PA10 / PB12 / PB13), it may lead to an overcurrent risk in the chip's GPIO  TRNG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                           | PXY pin connects to PXY_C pin in standby mode                                                                | Y      |            |  |

| SWD and JTAG debug function failure when using low power debug function  SWD connection fails when PA15 is low level  The analog watchdog threshold comparison fails when used simultaneously with oversampling in a 14-bit ADC  When using RTC reference clock detection function, PB13 / PB15 will be configured as input floating mode  Voltage or temperature changes in the backup domain cannot trigger the tamper function  TIMER TIMER interrupt is at risk of triggering by mistake  When USART FIFO is enabled, the last byte of the frame cannot be transmitted  When USART FIFO is enabled, DMA cannot transmit data  Data sample error occurs in LIN mode  In mute mode, the parity error caused by non-wake frames will set PERR bit  When I2S1 is used for communication and the GPIO and I2S1 configurations are in a special combination, it will probabilistically cause the I2S1_CK and I2S1_WS pins to continuously output signals  Interrupt and DMA functions are invalid when OSPI is used in indirect write mode  OSPI When OSPI sends only data segments, the first clock is lost Y  When OSPI running clock is greater than 100MHz, read external memory status flag abnormal in status polling mode  Auto refresh function of SDRAM controller is influenced by other EXMC controller  The bus may stuck during SDRAM access  Y Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | GPIO                      | be injected into GPIO (except for PA9 / PA10 / PB12 / PB13),                                                 | Y      | Υ          |  |

| DBG debug function  SWD connection fails when PA15 is low level  The analog watchdog threshold comparison fails when used simultaneously with oversampling in a 14-bit ADC  When using RTC reference clock detection function, PB13 / PB15 will be configured as input floating mode  Voltage or temperature changes in the backup domain cannot trigger the tamper function  TIMER TIMER interrupt is at risk of triggering by mistake  When USART FIFO is enabled, the last byte of the frame cannot be transmitted  When USART FIFO is enabled, DMA cannot transmit data  When USART FIFO is enabled, DMA cannot transmit data  Data sample error occurs in LIN mode  In mute mode, the parity error caused by non-wake frames will set PERR bit  When I2S1 is used for communication and the GPIO and I2S1 configurations are in a special combination, it will probabilistically cause the I2S1_CK and I2S1_WS pins to continuously output signals  Interrupt and DMA functions are invalid when OSPI is used in indirect write mode  OSPI When OSPI sends only data segments, the first clock is lost Y  When OSPI running clock is greater than 100MHz, read external memory status flag abnormal in status polling mode  Auto refresh function of SDRAM controller is influenced by other EXMC controller  The bus may stuck during SDRAM access  Y Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | TRNG                      | LFSR algorithm failure                                                                                       | Υ      |            |  |

| The analog watchdog threshold comparison fails when used simultaneously with oversampling in a 14-bit ADC  When using RTC reference clock detection function, PB13 / PB15 will be configured as input floating mode  Voltage or temperature changes in the backup domain cannot trigger the tamper function  TIMER  TIMER interrupt is at risk of triggering by mistake  When USART FIFO is enabled, the last byte of the frame cannot be transmitted  When USART FIFO is enabled, DMA cannot transmit data  When USART FIFO is enabled, DMA cannot transmit data  Y  In mute mode, the parity error caused by non-wake frames will set PERR bit  When I2S1 is used for communication and the GPIO and I2S1 configurations are in a special combination, it will probabilistically cause the I2S1_CK and I2S1_WS pins to continuously output signals  Interrupt and DMA functions are invalid when OSPI is used in indirect write mode  OSPI  When OSPI running clock is greater than 100MHz, read external memory status flag abnormal in status polling mode  Auto refresh function of SDRAM controller is influenced by other EXMC controller  The bus may stuck during SDRAM access  Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | DBG                       |                                                                                                              | N      |            |  |

| ADC  simultaneously with oversampling in a 14-bit ADC  When using RTC reference clock detection function, PB13 / PB15 will be configured as input floating mode  Voltage or temperature changes in the backup domain cannot trigger the tamper function  TIMER  TIMER interrupt is at risk of triggering by mistake  When USART FIFO is enabled, the last byte of the frame cannot be transmitted  When USART FIFO is enabled, DMA cannot transmit data  When USART FIFO is enabled, DMA cannot transmit data  In mute mode, the parity error caused by non-wake frames will set PERR bit  When I2S1 is used for communication and the GPIO and I2S1 configurations are in a special combination, it will probabilistically cause the I2S1_CK and I2S1_WS pins to continuously output signals  Interrupt and DMA functions are invalid when OSPI is used in indirect write mode  When OSPI running clock is greater than 100MHz, read external memory status flag abnormal in status polling mode  Auto refresh function of SDRAM controller is influenced by other EXMC controller  The bus may stuck during SDRAM access  Y  Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                           | SWD connection fails when PA15 is low level                                                                  | Y      |            |  |

| RTC    PB15 will be configured as input floating mode   Voltage or temperature changes in the backup domain cannot trigger the tamper function   N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ADC                       |                                                                                                              | Y      |            |  |

| USART  USART  IIMER interrupt is at risk of triggering by mistake  When USART FIFO is enabled, the last byte of the frame cannot be transmitted  When USART FIFO is enabled, DMA cannot transmit data  When USART FIFO is enabled, DMA cannot transmit data  V  Data sample error occurs in LIN mode  In mute mode, the parity error caused by non-wake frames will set PERR bit  When I2S1 is used for communication and the GPIO and I2S1 configurations are in a special combination, it will probabilistically cause the I2S1_CK and I2S1_WS pins to continuously output signals  Interrupt and DMA functions are invalid when OSPI is used in indirect write mode  OSPI When OSPI running clock is greater than 100MHz, read external memory status flag abnormal in status polling mode  Auto refresh function of SDRAM controller is influenced by other EXMC controller  The bus may stuck during SDRAM access  Y Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 570                       | •                                                                                                            | Y      |            |  |

| USART  When USART FIFO is enabled, the last byte of the frame cannot be transmitted  When USART FIFO is enabled, DMA cannot transmit data  Y  Data sample error occurs in LIN mode  In mute mode, the parity error caused by non-wake frames will set PERR bit  When I2S1 is used for communication and the GPIO and I2S1 configurations are in a special combination, it will probabilistically cause the I2S1_CK and I2S1_WS pins to continuously output signals  Interrupt and DMA functions are invalid when OSPI is used in indirect write mode  OSPI  When OSPI sends only data segments, the first clock is lost  When OSPI running clock is greater than 100MHz, read external memory status flag abnormal in status polling mode  Auto refresh function of SDRAM controller is influenced by other EXMC controller  The bus may stuck during SDRAM access  Y  Y   The bus may stuck during SDRAM access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | RIC                       |                                                                                                              | N      |            |  |

| USART  When USART FIFO is enabled, DMA cannot transmit data  When USART FIFO is enabled, DMA cannot transmit data  Data sample error occurs in LIN mode  In mute mode, the parity error caused by non-wake frames will set PERR bit  When I2S1 is used for communication and the GPIO and I2S1 configurations are in a special combination, it will probabilistically cause the I2S1_CK and I2S1_WS pins to continuously output signals  Interrupt and DMA functions are invalid when OSPI is used in indirect write mode  OSPI When OSPI sends only data segments, the first clock is lost Y  When OSPI running clock is greater than 100MHz, read external memory status flag abnormal in status polling mode  Auto refresh function of SDRAM controller is influenced by other EXMC controller  The bus may stuck during SDRAM access  Y  Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | TIMER                     | TIMER interrupt is at risk of triggering by mistake                                                          | Y      | Y          |  |

| Data sample error occurs in LIN mode  In mute mode, the parity error caused by non-wake frames will set PERR bit  When I2S1 is used for communication and the GPIO and I2S1 configurations are in a special combination, it will probabilistically cause the I2S1_CK and I2S1_WS pins to continuously output signals  Interrupt and DMA functions are invalid when OSPI is used in indirect write mode  OSPI When OSPI sends only data segments, the first clock is lost Y Y  When OSPI running clock is greater than 100MHz, read external memory status flag abnormal in status polling mode  Auto refresh function of SDRAM controller is influenced by other EXMC controller  The bus may stuck during SDRAM access Y Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                           |                                                                                                              | Y      |            |  |

| In mute mode, the parity error caused by non-wake frames will set PERR bit  When I2S1 is used for communication and the GPIO and I2S1 configurations are in a special combination, it will probabilistically cause the I2S1_CK and I2S1_WS pins to continuously output signals  Interrupt and DMA functions are invalid when OSPI is used in indirect write mode  When OSPI sends only data segments, the first clock is lost Y Y When OSPI running clock is greater than 100MHz, read external memory status flag abnormal in status polling mode  Auto refresh function of SDRAM controller is influenced by other EXMC controller  The bus may stuck during SDRAM access Y Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                           | When USART FIFO is enabled, DMA cannot transmit data                                                         | Y      |            |  |

| Will set PERR bit  When I2S1 is used for communication and the GPIO and I2S1 configurations are in a special combination, it will probabilistically cause the I2S1_CK and I2S1_WS pins to continuously output signals  Interrupt and DMA functions are invalid when OSPI is used in indirect write mode  When OSPI sends only data segments, the first clock is lost When OSPI running clock is greater than 100MHz, read external memory status flag abnormal in status polling mode  Auto refresh function of SDRAM controller is influenced by other EXMC controller  The bus may stuck during SDRAM access  Y  Y  Y  Y  Y  Y  Y  Y  Y  Y  Y  Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | USARI                     | Data sample error occurs in LIN mode                                                                         | Υ      | Υ          |  |

| Configurations are in a special combination, it will probabilistically cause the I2S1_CK and I2S1_WS pins to continuously output signals  Interrupt and DMA functions are invalid when OSPI is used in indirect write mode  When OSPI sends only data segments, the first clock is lost Y Y  When OSPI running clock is greater than 100MHz, read external memory status flag abnormal in status polling mode  Auto refresh function of SDRAM controller is influenced by other EXMC controller  The bus may stuck during SDRAM access Y Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                           |                                                                                                              | Y      | Y          |  |

| OSPI  When OSPI sends only data segments, the first clock is lost  When OSPI running clock is greater than 100MHz, read external memory status flag abnormal in status polling mode  Auto refresh function of SDRAM controller is influenced by other EXMC controller  The bus may stuck during SDRAM access  Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 128                       | configurations are in a special combination, it will probabilistically cause the I2S1_CK and I2S1_WS pins to | Y      | Y          |  |

| When OSPI running clock is greater than 100MHz, read external memory status flag abnormal in status polling mode  Auto refresh function of SDRAM controller is influenced by other EXMC controller  The bus may stuck during SDRAM access  Y  Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                           |                                                                                                              | Y      |            |  |

| EXMC  external memory status flag abnormal in status polling mode  Auto refresh function of SDRAM controller is influenced by other EXMC controller  The bus may stuck during SDRAM access  Y  Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | OSPI                      | When OSPI sends only data segments, the first clock is lost                                                  | Y      | Y          |  |

| EXMC other EXMC controller  The bus may stuck during SDRAM access  Y  Y  Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                           |                                                                                                              | Y      | Y          |  |

| The bus may stuck during SDRAM access Y Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <b>E</b> \(\(\text{1.5}\) |                                                                                                              | Y      |            |  |

| Does not support unaligned address access Y Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | EXMC                      | The bus may stuck during SDRAM access                                                                        | Υ      | Υ          |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                           | Does not support unaligned address access                                                                    | Υ      | Υ          |  |

|        | Limitations                                                                                                                                        |        | Workaround |  |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------|--------|------------|--|

| Module |                                                                                                                                                    |        | Rev.       |  |

|        |                                                                                                                                                    | Code A | Code C     |  |

| LPDTS  | The temperature sensor ready flag cannot be cleared after disabling LPDTS                                                                          | Y      |            |  |

|        | The transmit mailbox may experience transmission failures when exiting inactive mode                                                               | Y      |            |  |

|        | CAN transmit node performs unwanted automatic calibration                                                                                          | Y      |            |  |

|        | The CAN peripheral cannot function without using HXTAL                                                                                             | Y      |            |  |

|        | CAN RAM area may be tampered in receiving mailbox processing                                                                                       | Y      | Υ          |  |

| CAN    | After Bus off recovery, transmit error count is not cleared automatically                                                                          | Y      | Υ          |  |

|        | The mailbox data is not read in time may result in incorrect data reading for the current and next frames                                          | Y      | Υ          |  |

|        | When the CAN operating clock frequency is less than CK_APB2 and an error occurs in DLC segment, which will lead to receiving an incorrect frame ID | Y      | Υ          |  |

| USBHS  | USBHS OTG sensitivity problem                                                                                                                      | Y      |            |  |

### Note:

Y = Limitation present, workaround available

N = Limitation present, no workaround available

'--' = Limitation fixed

### 2. Descriptions of device limitations

### 2.1. SYSTEM

# 2.1.1. SysTick is clocked with the system clock (CK\_SYS) divided by 2 when using external clock source

### **Description & impact**

When SysTick uses external clock source, the SysTick clock is CK\_SYS / 2 instead of CK SYS / 8.

### Workarounds

Use CK SYS / 2 to calculate the SysTick time when using external clock source.

### 2.1.2. ECC error due to illegal address access

### **Description & impact**

When illegal address is accessed, CPU will generate ECC error.

### Workarounds

Use one of the following solutions:

- 1) Avoid accessing illegal addresses.

- Implement software processes to handle ECC errors after accessing an illegal address.

- 2.1.3. When the system operates at high frequency and both the interrupt vector table and interrupt handling code are placed in ITCM, high-frequency interrupts may probabilistically cause false ITCM ECC error alarm

### **Description & impact**

When the system clock is configured to a high frequency (e.g., 600MHz), the AXI/AHB clock is configured to half the system clock frequency, and TCM inserts wait states (TCM\_WAITSTATE = 1), placing both the interrupt vector table and interrupt handling code in ITCM may probabilistically cause false ITCM ECC error alarm when high-frequency interrupts occur.

Note: When the system clock exceeds 350MHz, TCM requires wait states to be inserted.

### Workarounds

Use one of the following solutions:

- Place the interrupt vector table in AXISRAM.